——DWIN Froum बाट साझा

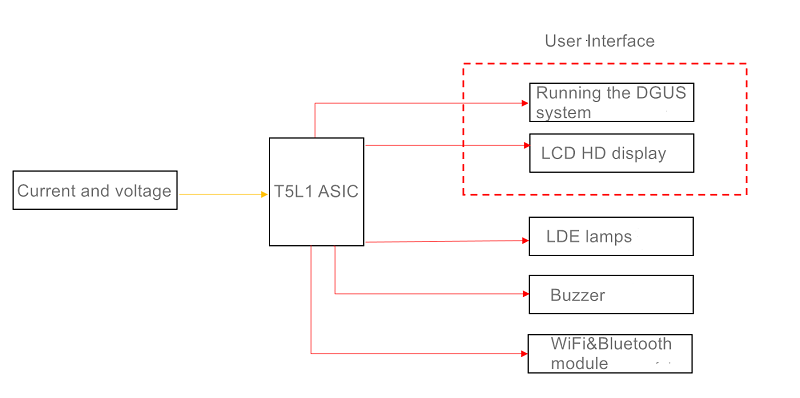

DWIN T5L1 चिपलाई सम्पूर्ण मेसिनको कन्ट्रोल कोरको रूपमा प्रयोग गरेर, टच, ADC अधिग्रहण, PWM नियन्त्रण जानकारी प्राप्त र प्रक्रिया गर्दछ, र वास्तविक समयमा वर्तमान स्थिति प्रदर्शन गर्न 3.5-इन्च LCD स्क्रिन ड्राइभ गर्दछ।वाइफाइ मोड्युल मार्फत एलईडी प्रकाश स्रोत चमक को रिमोट टच समायोजन समर्थन, र आवाज अलार्म समर्थन।

कार्यक्रम सुविधाहरू:

1. उच्च आवृत्तिमा चलाउन T5L चिप अपनाउनुहोस्, AD एनालग नमूना स्थिर छ, र त्रुटि सानो छ;

2. डिबगिङ र प्रोग्राम जलाउनको लागि PC मा सीधा जडान गरिएको TYPE C लाई समर्थन गर्नुहोस्;

3. समर्थन उच्च गति OS कोर इन्टरफेस, 16bit समानान्तर पोर्ट;UI कोर PWM पोर्ट, AD पोर्ट लीड आउट, कम लागत अनुप्रयोग डिजाइन, थप MCU थप्न आवश्यक छैन;

4. समर्थन वाइफाइ, ब्लुटुथ रिमोट नियन्त्रण;

5. समर्थन 5~12V DC चौडा भोल्टेज र फराकिलो दायरा इनपुट

1.1 योजना रेखाचित्र

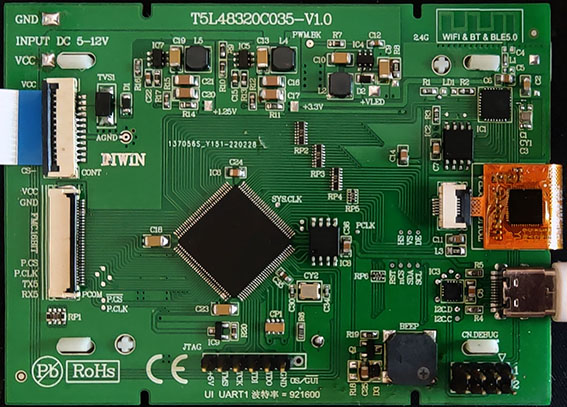

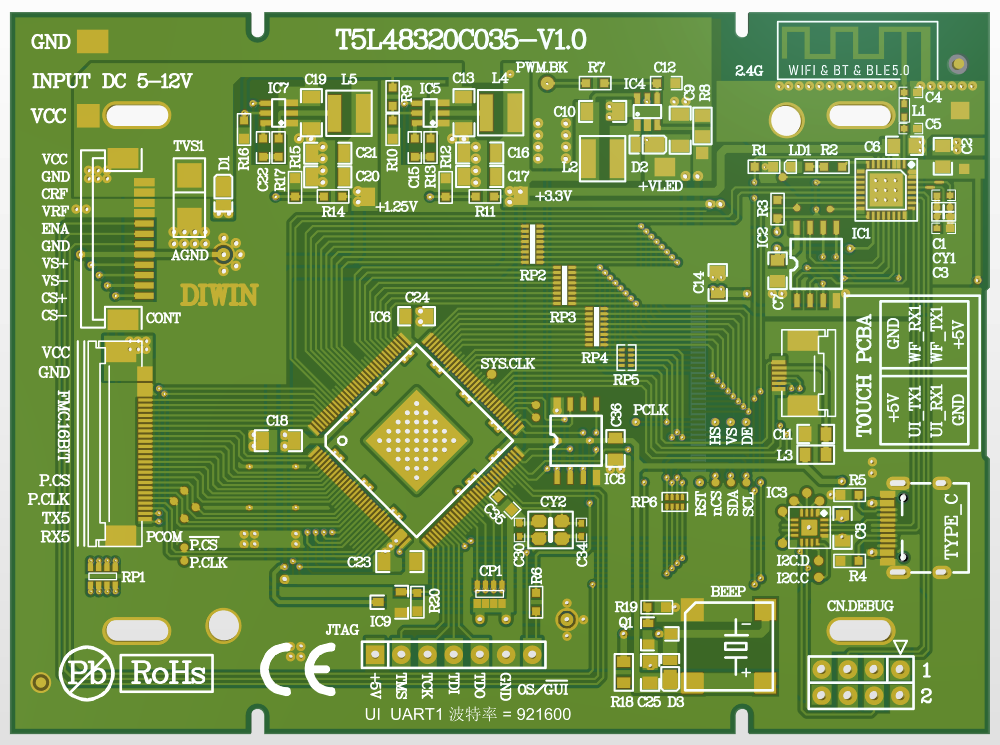

1.2 पीसीबी बोर्ड

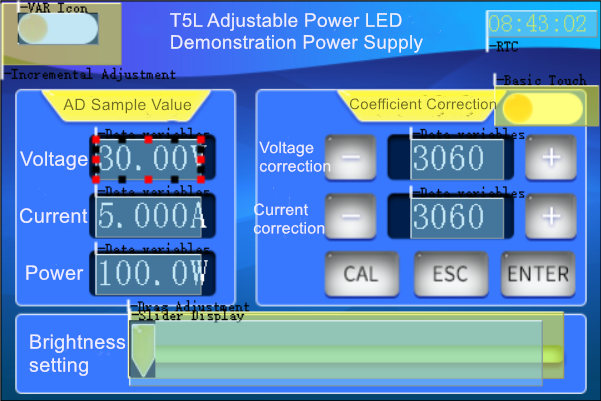

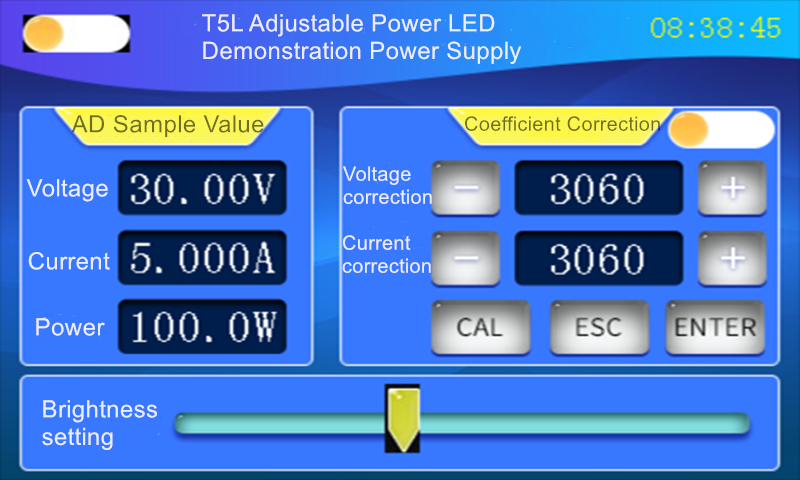

1.3 प्रयोगकर्ता इन्टरफेस

लज्जास्पद परिचय:

(1) हार्डवेयर सर्किट डिजाइन

1.4 T5L48320C035 सर्किट रेखाचित्र

1. MCU तर्क शक्ति आपूर्ति 3.3V: C18, C26, C27, C28, C29, C31, C32, C33;

2. MCU कोर पावर सप्लाई 1.25V: C23, C24;

3. MCU एनालग पावर सप्लाई 3.3V: C35 MCU को लागि एनालग पावर सप्लाई हो।टाइपसेटिङ गर्दा, कोर 1.25V ग्राउन्ड र लॉजिक ग्राउन्डलाई सँगै जोड्न सकिन्छ, तर एनालग ग्राउन्ड अलग हुनुपर्छ।एनालग ग्राउन्ड र डिजिटल ग्राउन्डलाई LDO आउटपुट ठूलो क्यापेसिटरको नकारात्मक पोलमा सङ्कलन गर्नुपर्छ, र एनालग सकारात्मक पोललाई LDO ठूलो क्यापेसिटरको सकारात्मक पोलमा पनि सङ्कलन गरिनुपर्छ, ताकि AD नमूना शोर कम हुन्छ।

4. AD एनालग सिग्नल अधिग्रहण सर्किट: CP1 AD एनालग इनपुट फिल्टर क्यापेसिटर हो।नमूना त्रुटि कम गर्नको लागि, MCU को एनालग ग्राउन्ड र डिजिटल ग्राउन्ड स्वतन्त्र रूपमा अलग गरिएको छ।CP1 को ऋणात्मक पोल न्यूनतम प्रतिबाधाको साथ MCU को एनालग ग्राउन्डमा जोडिएको हुनुपर्छ, र क्रिस्टल ओसिलेटरका दुई समानान्तर क्यापेसिटरहरू MCU को एनालग ग्राउन्डमा जोडिएका छन्।

5. बजर सर्किट: C25 बजरको लागि पावर सप्लाई क्यापेसिटर हो।बजर एक प्रेरक यन्त्र हो, र त्यहाँ सञ्चालनको समयमा शिखर वर्तमान हुनेछ।शिखरलाई कम गर्नको लागि, MOS ट्यूबलाई रैखिक क्षेत्रमा काम गर्नको लागि बजरको MOS ड्राइभ वर्तमान कम गर्न आवश्यक छ, र यसलाई स्विच मोडमा काम गर्न सर्किट डिजाइन गर्नुहोस्।ध्यान दिनुहोस् कि बजरको ध्वनि गुणस्तर समायोजन गर्न र बजरको आवाज कुरकुरा र रमाइलो बनाउन R18 लाई बजरको दुवै छेउमा समानान्तर रूपमा जडान गरिएको हुनुपर्छ।

6. WiFi सर्किट: WiFi चिप नमूना ESP32-C, WiFi+Bluetooth+BLE सँग।तारमा, आरएफ पावर ग्राउन्ड र सिग्नल ग्राउन्ड अलग गरिएको छ।

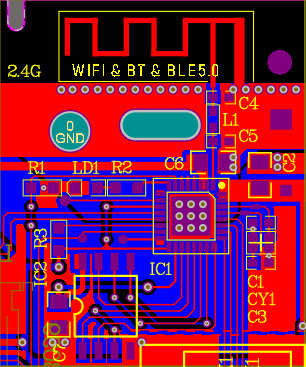

1.5 वाइफाइ सर्किट डिजाइन

माथिको चित्रमा, तामाको कोटिंगको माथिल्लो भाग पावर ग्राउन्ड लूप हो।WiFi एन्टेना प्रतिबिम्ब ग्राउन्ड लूपमा पावर ग्राउन्डमा ठूलो क्षेत्र हुनुपर्छ, र पावर ग्राउन्डको सङ्कलन बिन्दु C6 को नकारात्मक पोल हो।पावर ग्राउन्ड र वाइफाइ एन्टेनाको बीचमा प्रतिबिम्बित वर्तमान प्रदान गर्न आवश्यक छ, त्यसैले त्यहाँ वाइफाइ एन्टेना मुनि तामा कोटिंग हुनुपर्छ।तामाको कोटिंगको लम्बाइ वाइफाइ एन्टेनाको विस्तार लम्बाइभन्दा बढी छ, र विस्तारले वाइफाइको संवेदनशीलता बढाउनेछ;C2 को ऋणात्मक ध्रुवमा बिन्दु।तामाको ठूलो क्षेत्रले वाइफाइ एन्टेना विकिरणले गर्दा हुने आवाजलाई जोगाउन सक्छ।२ तामाको आधार तलको तहमा छुट्याइन्छ र ESP32-C को मध्य प्याडमा viaas मार्फत जम्मा गरिन्छ।RF पावर ग्राउन्डलाई सिग्नल ग्राउन्ड लूप भन्दा कम प्रतिबाधा चाहिन्छ, त्यसैले पर्याप्त रूपमा कम प्रतिबाधा सुनिश्चित गर्न पावर ग्राउन्डबाट चिप प्याडमा 6 वटा भियाहरू छन्।क्रिस्टल ओसिलेटरको ग्राउन्ड लुपमा आरएफ पावर प्रवाह हुन सक्दैन, अन्यथा क्रिस्टल ओसिलेटरले फ्रिक्वेन्सी जिटर उत्पन्न गर्नेछ, र वाइफाइ फ्रिक्वेन्सी अफसेटले डेटा पठाउन र प्राप्त गर्न सक्षम हुनेछैन।

7. ब्याकलाइट एलईडी पावर सप्लाई सर्किट: SOT23-6LED चालक चिप नमूना।LED लाई DC/DC बिजुली आपूर्तिले स्वतन्त्र रूपमा लुप बनाउँछ, र DC/DC ग्राउन्ड 3.3V LOD ग्राउन्डमा जोडिएको छ।PWM2 पोर्ट कोर विशेष गरिएको छ, यसले 600K PWM सिग्नल आउटपुट गर्दछ, र PWM आउटपुटलाई ON/OFF नियन्त्रणको रूपमा प्रयोग गर्नको लागि RC थपिएको छ।

8. भोल्टेज इनपुट दायरा: दुई DC/DC स्टेप-डाउन डिजाइन गरिएको छ।नोट गर्नुहोस् कि DC/DC सर्किटमा R13 र R17 प्रतिरोधकहरू हटाउन सकिँदैन।दुई DC/DC चिपहरूले 18V इनपुट सम्म समर्थन गर्दछ, जुन बाह्य विद्युत आपूर्तिको लागि सुविधाजनक छ।

9. USB TYPE C डिबग पोर्ट: TYPE C लाई अगाडि र पछाडि प्लग गर्न र अनप्लग गर्न सकिन्छ।अगाडि सम्मिलनले WIFI चिप ESP32-C सँग WIFI चिप प्रोग्राम गर्न संचार गर्दछ;रिभर्स इन्सर्सनले T5L कार्यक्रम गर्न XR21V1410IL16 सँग सञ्चार गर्छ।TYPE C ले 5V पावर सप्लाई समर्थन गर्दछ।

10. समानान्तर पोर्ट संचार: T5L OS कोरमा धेरै नि: शुल्क IO पोर्टहरू छन्, र 16bit समानान्तर पोर्ट संचार डिजाइन गर्न सकिन्छ।ST ARM FMC समानान्तर पोर्ट प्रोटोकलसँग संयुक्त, यसले सिंक्रोनस पढ्न र लेख्न समर्थन गर्दछ।

11. LCM RGB हाई-स्पीड इन्टरफेस डिजाइन: T5L RGB आउटपुट सीधा LCM RGB मा जडान गरिएको छ, र LCM पानी लहर हस्तक्षेप कम गर्न बीचमा बफर प्रतिरोध थपिएको छ।तारिङ गर्दा, RGB इन्टरफेस जडानको लम्बाइ घटाउनुहोस्, विशेष गरी PCLK सिग्नल, र RGB इन्टरफेस PCLK, HS, VS, DE परीक्षण बिन्दुहरू बढाउनुहोस्;स्क्रिनको SPI पोर्ट T5L को P2.4~P2.7 पोर्टहरूसँग जोडिएको छ, जुन स्क्रिन ड्राइभर डिजाइन गर्नको लागि सुविधाजनक छ।अन्तर्निहित सफ्टवेयरको विकासलाई सहज बनाउन RST, nCS, SDA, SCI परीक्षण बिन्दुहरूको नेतृत्व गर्नुहोस्।

(2) DGUS इन्टरफेस

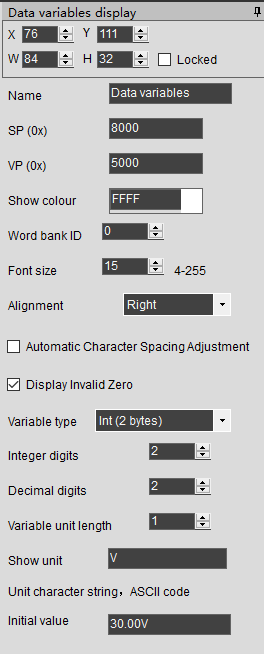

1.6 डाटा चर प्रदर्शन नियन्त्रण

(३) ओएस

//—————————— DGUS पढ्ने र लेख्ने ढाँचा

typedef संरचना

{

u16 addr;//UI 16bit चर ठेगाना

u8 datLen;//8 बिटडेटा लम्बाइ

u8 *pBuf;//8 बिट डाटा सूचक

} UI_packTypeDef;//DGUS पढ्नुहोस् र प्याकेट लेख्नुहोस्

//——————————- डाटा चर प्रदर्शन नियन्त्रण

typedef संरचना

{

u16 VP;

u16 X;

u16 Y;

u16 रंग;

u8 Lib_ID;

u8 फन्ट साइज;

u8 algnment;

u8 IntNum;

u8 DecNum;

u8 प्रकार;

u8 LenUint;

u8 StringUinit [११];

} Number_spTypeDef;// डाटा चर विवरण संरचना

typedef संरचना

{

Number_spTypeDef sp;// SP वर्णन सूचक परिभाषित गर्नुहोस्

UI_packTypeDef spPack;// SP चर DGUS पढ्न र लेख्ने प्याकेज परिभाषित गर्नुहोस्

UI_packTypeDef vpPack;// vp चर DGUS पढ्न र लेख्ने प्याकेज परिभाषित गर्नुहोस्

} Number_HandleTypeDef;// डाटा चर संरचना

अघिल्लो डाटा चर ह्यान्डल परिभाषा संग।अर्को, भोल्टेज नमूना प्रदर्शनको लागि एक चर परिभाषित गर्नुहोस्:

Number_HandleTypeDef Hsample;

u16 voltage_sample;

पहिले, प्रारम्भिक कार्य कार्यान्वयन गर्नुहोस्

NumberSP_Init(&Hsample, भोल्टेज_sample,0×8000);//0×8000 यहाँ वर्णन सूचक हो

//——एसपी सूचक संरचना प्रारम्भिकता देखाउँदै डाटा चर ——

void NumberSP_Init(Number_HandleTypeDef *number,u8 *value, u16 numberAddr)

{

number->spPack.addr = numberAddr;

number->spPack.datLen = sizeof(number->sp);

number->spPack.pBuf = (u8 *)&number->sp;

Read_Dgus(&number->spPack);

number->vpPack.addr = number->sp.VP;

switch(number->sp.Type) //vp चरको डेटा लम्बाइ DGUS इन्टरफेसमा डिजाइन गरिएको डाटा भेरिएबल प्रकार अनुसार स्वचालित रूपमा चयन हुन्छ।

{

केस ०:

केस ५:

नम्बर->vpPack.datLen = 2;

ब्रेक;

केस १:

केस २:

केस ३:

केस ६:

नम्बर->vpPack.datLen = 4;

केस ४:

नम्बर->vpPack.datLen = 8;

ब्रेक;

}

number->vpPack.pBuf = मान;

}

प्रारम्भ पछि, Hsample.sp भोल्टेज नमूना डेटा चरको विवरण सूचक हो;Hsample.spPack DGUS इन्टरफेस प्रकार्य मार्फत OS कोर र UI भोल्टेज नमूना डेटा चर बीचको संचार सूचक हो;Hsample.vpPack भोल्टेज नमूना डेटा चर परिवर्तन गर्ने विशेषता हो, जस्तै फन्ट रङहरू, आदि पनि DGUS इन्टरफेस प्रकार्य मार्फत UI कोरमा पठाइन्छ।Hsample.vpPack.addr भोल्टेज नमूना डेटा चर ठेगाना हो, जुन स्वतः प्रारम्भिक प्रकार्यबाट प्राप्त गरिएको छ।जब तपाइँ DGUS इन्टरफेसमा चर ठेगाना वा चल डाटा प्रकार परिवर्तन गर्नुहुन्छ, OS कोरमा सिंक्रोनस रूपमा चल ठेगाना अद्यावधिक गर्न आवश्यक पर्दैन।OS कोरले voltage_sample चर गणना गरेपछि, यसलाई अपडेट गर्न Write_Dgus(&Hsample.vpPack) प्रकार्य मात्र कार्यान्वयन गर्न आवश्यक छ।DGUS प्रसारणको लागि voltage_sample प्याक गर्न आवश्यक छैन।

पोस्ट समय: जुन-15-2022